|

| Elliott Sound Products | Project 237 |

Main Index Main Index

Projects Index Projects Index

|

One could be excused for thinking that I don't like JFETs, since they aren't used in many projects. I've also criticised their wide parameter spread in Designing With JFETs and elsewhere. However, I don't dislike JFETs at all, and if the JFETs that I used (and liked) ages ago were still available, there would be more projects featuring them. Unfortunately, there are fewer and fewer JFETs available every year. Some are still available in SMD, but many seem to have simply vanished without a trace.

If you do a web search, you'll find any number of test circuits for JFETs. Some use an opamp to buffer the output, some use one to apply bias, but none that I've seen uses a servo circuit to set the operating conditions precisely for each device being tested. This tester is different, in that the servo adjusts the source voltage to obtain a fixed (nominally 6V) voltage on the drain, but allows the bias to be adjusted while maintaining the same impedances throughout so each device can be individually be characterised. It's not necessarily 'better' than the other circuits I've seen, but it does ensure that each JFET tested 'sees' an almost identical impedance at each terminal. The only thing that's changed is the voltage at the source terminal - the impedance remains the same regardless of voltage, and the quiescent drain current doesn't change from one DUT (device under test) to the next. You choose the drain current by using an appropriate resistor value (switched or plug-in). In the article referenced above, I said that the idea of using a servo to bias a JFET was 'silly', but as shown here it's not even a little bit silly.

Rather than just providing the basic data to allow you to design the stage, this tester (almost) designs the stage for you. Parameter spread is always the biggest hurdle to implementing a JFET into any project. The two main things that vary widely are the pinch-off voltage (VGS (off)), which is the voltage required to turn the JFET off, typically taken as the voltage that reduces ID (drain current) to somewhere between 1nA and 1µA (or thereabouts). The other is IDSS, the drain current with zero volts between the gate and source (VGS).

Both can vary by as much as 10:1, depending on the device. To make a 'universal' tester, a means of setting the bias voltage is needed, ideally without you having to do anything other than plug the JFET into the test terminals. As noted above, the general idea was presented in the 'Designing With JFETs' article. Something that was revealed during testing the circuit described is that while parameter spread is very real, it isn't always quite as bad as it seems at first, but only when you use a biasing system that adjusts itself for the JFET under test.

There is still considerable variance though, and two JFETs of the same type (and grade if applicable) can give up to 3dB gain variation in (more-or-less) identical circuits. The idea of this tester is that the JFETs are tested under operating conditions, rather than working with the two major parameters - VGS (off) and IDSS. The input and output are both AC and can be viewed on a scope, and the value of VGS needed for the selected drain current is also available as a DC value. This is far simpler than having VGS (off) and IDSS available, because with those you still have to calculate appropriate values for the source and drain resistors.

The original design was set up for N-Channel FETs, and it requires a few extra parts and modification to work with P-Channel devices. Fortunately only the drain voltage and opamp reference need to be changed (from positive to negative). The opamp will then adjust itself automatically. This is included in the project version.

The tester uses an opamp (e.g. TL072 or similar) as an integrator/ bias servo, which sets the drain voltage to exactly half the supply voltage, nominally 6V for a 12V supply. The other half of the opamp is used as a buffer so you can take measurements without loading the JFET. When a JFET is installed, the opamp adjusts the bias voltage to provide the exact VGS needed to get 6V at the drain. Sw2 is used to select between N-Channel and P-Channel FETs. The circuit is not limited to JFETs, and it will also work with small-signal MOSFETs (e.g. 2N7000) or even a bipolar transistor (BJT).

The tester will work with most JFETs, but there can be 'outliers' that cannot be biased because the opamp can't raise the source voltage far enough. For example, if a JFET needs a VGS of 6V on the source, there's no voltage across the FET because the drain voltage is also 6V. Mostly, changing the drain current will bring it back into range. If possible, aim for a drain current between 50% and 80% of IDSS, both for testing and in use.

To combat this, you can change the drain resistance to the +ve supply. I've shown three nominal settings, 600µA, 1mA and 2.7mA. These can be changed (or more ranges added) to suit your test requirements. You could even use a pot (with a series resistor of ~220Ω), but that should not be needed for most common tests. Needless to say, you can adapt the circuit for any test parameters you like. The DC supply should be turned off when changing FETs, as the bias servo will charge C1 to around -11V with no device installed. It takes about 5 seconds for the bias to stabilise due to the servo's slow reaction. The alternative to switched ranges (and the method I used) is a pair of machine sockets, allowing you to install any resistor or current source 'diode' (more on that below).

The circuit (deliberately) has no facility to linearise the JFET - it's designed without AC feedback to let you test those you have available to determine the biasing requirements and measure the gain. The bias voltage (VGS) is available on a separate output, and can be measured with a multimeter. For example, if you install a device and read 1.5V at the VGS output, you know that the gate bias voltage is -1.5V for the selected current. You can also monitor the output on an oscilloscope to see the output waveform, which is buffered by U1B to present a low output impedance (useful for connecting a distortion analyser). Note that C1 is a bipolar electrolytic cap, needed because the voltage is reversed when testing N- or P-Channel FETs, and it also changes if you test a MOSFET.

If you don't need to test P-Channel FETs, the polarity switching (and negative reference) can be omitted. The 'Power On' LED is optional. The lower frequency limit is set by C1 (-3dB at 16Hz), but most tests will probably be carried out at 400Hz or more. The value can be increased if you wish. The performance of any DUT at low frequencies (including DC) is close to identical to that at a 'sensible' test frequency, and there's no need to verify it with the tester. Low-frequency performance depends on your final circuit.

I've shown the drain resistors (RD a,b,c) connected to the 12V supply, but they can go to another external voltage if you wish. The reference voltage should be altered to suit your requirements, but with the values shown you can use supplies of up to ±15V, or even a little higher (the TL072 is limited to ±18V absolute maximum). You could also use a higher voltage opamp - they exist, but are expensive. Example voltages are shown in green, but the gate voltage (0V) and the drain voltage (+6V) are fixed, and only the source voltage (shown as +300mV) will change. It should always be positive for a JFET.

I recommend that you use a section of IC socket or separate machined sockets to allow FETs (and/ or drain resistors) to be plugged in without soldering. If you're selecting FETs for matching, then you'll most likely go through quite a few before you find two the same. The advantage of this tester is that it lets you look at the VGS under realistic operating conditions, and you can also verify the gain on a scope or AC millivoltmeter. Note that different JFET types have different pinouts, and it will be necessary to swap the leads around to suit. Most JFETs are symmetrical, and you can exchange drain and source with no change in performance. This doesn't apply to all, but it's easy to test. I tested a J113 and 2SK170 both 'normal' and 'reversed', and the results were identical.

The input level will have to be adjusted to suit the JFET and drain resistance. Mostly, it will be between 10-100mV (peak or RMS) - bearing in mind that you have to stay well below clipping or visible distortion for the results to be meaningful. The gain will be highest when the '0.6m' ID setting is used, because the resistance is highest. It is possible to use a current source rather than a resistor for the load, but that's made more complex due to the need for testing N-Channel and P-Channel JFETs. That would mean two separate current sources of opposite polarities, which makes switching (and the overall project) much more complex. If you use sockets for RD, you can plug in constant-current diodes instead of resistors. These will increase the measured gain by up to 10 times.

The inset shows how to create a JFET current source. The JFET and resistor are both 'SOT' (select on test), and are selected to get the desired current, preferably with the least voltage drop across RS. The 'constant current diodes' (aka CRD [current regulating diode] or CLD [current limiting diode]) you can buy from major suppliers are nothing more than the circuit shown, either with or without the resistor [ 3 ]. You'll probably have to experiment to get the current you need. RS can be a trimpot if preferred. Use of a current source load will increase the gain of the DUT quite dramatically (by a factor of ×5-10). With a BJT, expect an AC gain of anything from 500 to over 1,000, or as much as 2,500 for a 2N7000 MOSFET!

Something that is potentially useful is to use asymmetrical supplies. The negative supply could be (say) 5V, with 25V for the positive supply. This keeps the opamp happy, but lets you test at higher voltages (in this case, the drain voltage will be 12.5V rather than 6V. Increasing the drain voltage and current will increase the gain of a JFET (in most cases), and may let you get closer to normal operating voltages for your final circuit. If you do this and run a test on multiple JFETs, make sure that you include the test conditions in your tabled results!

While it's not particularly useful, you can plug a BJT into the test socket, and the auto-bias servo will set it up so it will work too. It will also bias MOSFETs, and is potentially useful for small-signal types. You can test high frequency response, but the opamp will be the limiting factor. Of course you can add a test point to allow you to connect a ×10 scope probe directly to the JFET's drain for high frequency analysis if that's something you need.

Some distortion is evident in the above graph, shown by the fact that negative and positive half-cycles are at different amplitudes. The simulator says that THD is just under 2.9%, and is comprised of 2nd and 3rd harmonics, with little of consequence above that (remaining harmonics are below -100dB). This is typical of JFETs, and to get accurate results the input voltage should be reduced from 140mV (as tested) to about 20mV (~200mV RMS output). The circuit is designed to allow you to test a number of FETs quickly, without having to mess around with a bias circuit. Once you have characterised the FETs in your collection, you know what they can do, and you know the optimum bias level. All tests are performed at exactly the same current, because the servo ensures that the average voltage across the selected drain resistor remains constant.

The tester is not designed to characterise performance - it's intended only to let you sort your collection using 'sensible' values (your definition of 'sensible' may vary  ). The final values used depend on the circuit you're using, and just how the JFET is configured (gain stage, follower, cascode, etc.).

). The final values used depend on the circuit you're using, and just how the JFET is configured (gain stage, follower, cascode, etc.).

In use, the peak input voltage to a JFET stage cannot exceed VGS by more than a couple of hundred millivolts at most. If the input level is such that it forward-biases the gate diode, you have gate current (highly undesirable) and the result will be severe distortion. In any final design, it's up to you to ensure that the voltages are acceptable. You can use the tester for this, by increasing the input voltage until you see a distorted output. About 1% THD is visible on a scope. Table 1 (shown below) has the measured VGS, voltage gain and other parameters for ten 2SK170 JFETs.

In the Designing With JFETs article, I showed a simple static tester (reproduced above), and that will let you get the basic parameters. You can work out the values needed for a design from these, but unlike the Fig. 1 version, tests are purely static. With Sw1 open, the external meter shows VGS (off), the voltage at which minimal current flows (just through R2). For example, if you measure VGS (off) at 1.2V, the voltage is measured with a current of 1.2µA (because R2 is a 1MΩ resistor). This is almost always accurate enough for basic tests. When Sw1 is closed, the maximum current flows (IDSS). Since R1 is a 1Ω resistor, the voltage is equal to the current, so (for example) 3.5mV means 3.5mA. R1 can be increased to 10Ω if you have difficulty reading very low voltages, but you have to divide the voltage by ten (3.5mA would give a reading of 35mV with a 10Ω resistor). Sw1 must have very low (and consistent) contact resistance.

R3 is a 'safety' resistor. It will have a (very) small effect on your readings, but it's there to protect your power supply against a (close to) dead short if the FET is faulty or inserted incorrectly. As shown it's set up for N-Channel FETs, and P-Channel devices simply require the supply polarity to be reversed.

JFETs are normally said to be operated in the 'saturation' region, which is to say that the device will draw the maximum current possible for a given (negative) gate voltage. This doesn't mean that changing the drain voltage won't affect the current, because it will. The amount of change depends on the JFET itself, and (like all parameters) it will vary from one device to the next - even of the same type. The current change over a range of (say) 20V can vary by as much as 10mA or less than 50µA. A source resistor (as shown in the inset of Fig. 1) is required if you need stable current vs. voltage.

The maximum current for any JFET is defined by IDSS, the current drawn with zero gate-source voltage. It should be apparent that expecting to operate a JFET with an IDSS of 1mA with a drain current of more than 1mA won't work - ideally the quiescent drain current will be somewhere between 50% and 85% of the rated (or measured) IDSS for minimum distortion. This isn't always possible.

Using the Fig. 1 tester's results, you can calculate the gm (aka forward transconductance, |Yfs|, etc.). For example, if you use the 1mA range (actually 1.07mA) and you see a voltage change of 300mV, that equates to a current change of 54µA through the 5.6kΩ resistor). The output voltage waveform should be visibly free of distortion - generally it becomes visible on a scope at around 1%. Transconductance is determined by the change (Δ) of drain current vs. the change of gate voltage. If the input voltage change were 20mV, the gm is ...

gm = ΔID / ΔVG

gm = 54µ / 20m = 2.7mS (milli-Siemens) = 2.7mA/V

The voltages and currents measured/ calculated can be RMS, peak or peak-to-peak. In general, you need to ensure that the output voltage is at a sensible level by adjusting the input voltage. Transconductance is not a fixed number, and it depends on the drain current. If you were to be sorting a number of JFETs, it would be useful to create a simple spreadsheet that will make the calculations for you, based on your measurements. Your JFETs can then be marked with a number that relates them to the spreadsheet entry. You'd also include the VGS used for the tests, and you'd have the info you need to use them in a project. It's a fair bit of messing around, but at least you have the data you need to use them. No other device requires this unless you're searching for true matched pairs, but it's always necessary with JFETs unless you include trimpots to set the bias and gain.

I tested a number of 2SK170 (GR) JFETs that I have in stock. I've had these for ages, and have tested a few for other JFET articles. When you look at the datasheet, the parameter spread is wide (as we expect of JFETs). IDSS ranges from 2.6 to 20mA, and VGS (off) ranges from -200mV to -1.5V. If you use the 'common' test procedures (using the Fig. 3 test circuit for example), you will see the spread, even though the JFETs I used are 'graded'. Common IDSS grades for 2SK170 JFETs are 'GR' (2.6~6.5mA), 'BL' (6.0~12mA) and 'V' (10~20mA).

When the 'proper' tester is used (Fig. 1), I obtained the following results. This demonstrates that 'real life' isn't as clear cut as we might think, and the variance in an actual circuit isn't as great as you may have expected. However, there's still a variance of 0.59dB in gain from the lowest to highest. That means you must either include a gain adjust trimpot or select devices carefully for a stereo preamplifier. We expect (and usually get) gain to within 0.1dB between stereo channels, but if you use random JFETs this is easily exceeded. If you check the table results, you'll see that no two 2SK170s have exactly the same gain. The 'AV' column is/ was common in valve datasheets, and it stands for 'Amplification, voltage'. I used a 3.6kΩ resistor for RD.

| No. | VOut (mV) | VGS (mV) | AV | dB | Δ I (mA) | gm (mS) |

| 1 | 780 | 297 | 39 | 31.82 | 0.22 | 10.83 |

| 2 | 794 | 218 | 39.7 | 31.98 | 0.22 | 11.03 |

| 3 | 800 | 157 | 40 | 32.04 | 0.22 | 11.11 |

| 4 * | 805 | 222 | 40.25 | 32.1 | 0.22 | 11.18 |

| 5 | 827 | 157 | 41.35 | 32.33 | 0.23 | 11.49 |

| 6 | 782 | 267 | 39.1 | 31.84 | 0.22 | 10.86 |

| 7 | 773 | 283 | 38.65 | 31.74 | 0.21 | 10.74 |

| 8 | 785 | 253 | 39.25 | 31.88 | 0.22 | 10.90 |

| 9 | 784 | 259 | 39.2 | 31.87 | 0.22 | 10.89 |

| 10 * | 808 | 228 | 40.4 | 32.13 | 0.22 | 11.22 |

| Max | 827 | 297 | 41.35 | 32.33 | 0.23 | 11.49 |

| Min | 773 | 157 | 38.65 | 31.74 | 0.21 | 10.74 |

I used 2SK170 JFETs, but the only way now to ensure that you get what you pay for is to use LSK170 JFETs from Linear Systems (they have many others too, and are one of the few remaining sources for high-performance, low-noise JFETs). Note in particular JFETs #3 and #5 - they have the same VGS, yet their gains (and gm) are different. Not by a great deal, but that shows that you can't rely on one parameter to predict others. From the table, it's easy to determine the required source resistance to bias the FET to match the test conditions (specifically the drain current). It's simply VGS / ID. If we take FET #1, that works out to ...

RS = VGS / ID

RS = 0.297V / 1.67mA = 178 Ω (Use 180 Ω)

Note: Always verify that the gate voltage (VGS) is positive. Some combinations of JFETs and drain resistance may result in the servo pushing the source voltage negative in an attempt to set up the bias conditions. The absolute maximum allowable negative voltage is about 400mV (less is better), after which the gate-source diode will conduct. With more than 400mV, expect to see little or no AC output, with the likelihood of serious distortion. BJTs and MOSFETs are the opposite, and will always have a negative base/ gate voltage.

To get the gain shown in the table, the source resistor must be bypassed. If it's not bypassed, the gain will be lower, and there is a small amount of degeneration. This will improve linearity (a little), and if the same value resistor is used with the two closest JFETs (#4 and #10 as indicated for example) the gain will be as close as you can get it without adjustment. Because of the low resistance, a bypass cap needs to be BIG, needing about 1mF (1,000µF) to get flat response to 10Hz (-3dB at 1Hz). The tester uses a 10µF bypass cap, as it's intended to be used at 400Hz or 1kHz.

Of all the tests I've carried out on JFETs over the years, this tester is by far the best way to characterise each device. The drain current can be set for anything you choose, and the tester will indicate very quickly if you will get close to the results you're looking for. My tester has a pair of 'machine sockets' (also used for the DUT) instead of switched drain resistors, so I can install anything that looks like it might work. If it can't be biased with any selected value, it's only a matter of changing the resistance and trying again.

Since I said that the tester will also bias BJTs and MOSFETs, I tried a BC549 and a 2N7000. The BJT came in with a gain of 156.8 (43.9dB) with 6mA collector current. The input voltage had to be reduced to 5mV for the test. The 2N7000 was also tested at 6mA, and had a voltage gain of 28.3 (29dB). In both of these cases, the voltage measured as VGS was negative, because the base/ gate voltage has to be positive referred to the emitter or source.

A 2SK170 (GR) tested at 6mA required a VGS of only 54mV, which indicates that it will just achieve the claimed maximum of 6.5mA with zero source resistance. The voltage gain (AV) measured 19.55, or 25.8dB. The peak input voltage should not exceed 50mV (less than 1V peak output).

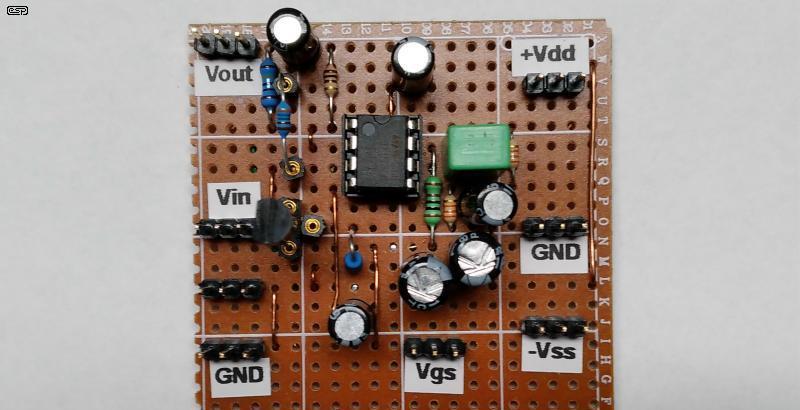

Fig. 4 shows my prototype, in all its Veroboard glory. It's not flash, and will almost certainly never get a case or its own power supply. This is one of those things that I won't need often, but I had to build one so I could verify that it does what I claim for it. Not just for readers, but for myself. I'm pretty confident that my simulations represent reality fairly closely, but any given device in the simulator is identical when placed, so five instances of a JFET will all be perfectly matched.

What came as a surprise when I used the tester was that the JFETs I checked were as close as they turned out to be. The values for VGS (off) and IDSS differ widely, but the gain when set up in the tester is remarkably consistent (for JFETs). However, the gain spread is still excessive if you were to be building a stereo preamp, and additional circuitry would normally be added to provide much higher open-loop gain, with the final gain set by negative feedback. Either that, or a trimpot would have to be added to allow the gain to be trimmed until both channels were the same.

As you may expect, you can't use the same bias resistor value in all cases if you expect a particular drain voltage and current. The values needed for the JFETs in the table vary over a range of almost 2:1, and that's enough to cause two channels of a preamp to be quite different from each other

The circuit shown in Fig. 1 is the simplest way to use a servo to bias a JFET. It's not the only way though, as it's possible to use an inverting servo that provides a negative voltage to the gate. This has the advantage that the full 12V is always across the test circuit, but it needs particularly good filtering to prevent negative feedback from altering the measured results. After several tests, I decided that the circuit shown is preferable, because it uses the DUT in the same way it will be used in a circuit. An inverting servo also requires an input capacitor. This isn't a major hurdle, but the circuit is a little less intuitive.

JFETs will always cause people grief, primarily due to the wide parameter spread. Even 'high end' devices have the same problem, and it makes designs harder than they should be. There are countless websites that provide every formula you'll (n)ever need, but if you can't measure the actual parameters (as opposed to the nominal range provided in the datasheet), the formulae are entirely useless. Applications that use low-noise JFETs in parallel require that each FET is as close to identical to the others as you can get. This isn't easy without a means of testing them thoroughly.

I've always preferred a practical approach where possible. A means of characterising devices is very useful, as it lets you match devices to the extent needed for the application. Matching can be a tedious process, but a test set like that described here makes it a lot easier than would otherwise be the case. It will still be tedious, but at the end you'll have 'sets' of matched JFETs ready for your next project. There will be 'outliers' that have no match, but they can still be characterised and used where only a single device is needed.

There really is something 'nice' about JFETs, especially for someone (like me) who grew up at the tail end of the valve (vacuum tube) era. I rarely specify them because all of the common types of linear JFETs (as opposed to switching types) have mysteriously vanished from major vendors' websites, with only a relatively small number of 'hobbyist' suppliers offering them. Their provenance is unknown though - yes, you'll get a JFET, but it may not be the type that's printed on the case. 'Auction' sites have numerous vendors (mostly from China) who can supply a package with any number you like printed on it. What's inside is anyone's guess.

The test tools described here will let you find out their characteristics for the most part, but testing for low noise (for example) will still be a challenge. It's possible, but you would probably need to make some changes to the circuit to make such tests usable. This may come later. The main problem when measuring noise is extraneous noise from the now common array of switchmode supplies used in most modern test equipment. The entire servo system would need to be in an earthed shielding enclosure, with supply filtering to eliminate as much external noise as possible.

The above ESP articles have additional references, so they're not shown again here. As far as I'm aware, the 'auto-bias' servo amplifier circuit is original.

Main Index Main Index

Projects Index Projects Index

|